반도체 종류

메모리반도체

종류

D램

낸드플래스

제조사

삼성전자

sk하이닉스

마이크론

시스템반도체(비메모리)

ARM: 특허 (원천)

설계: 애플, 엔비디아, 퀄컴, 테슬라, 미디어텍, NXP, LX세미콘, 삼성전자

제조(파운드리): TSMC, 삼성전자, UMC, DB하이텍

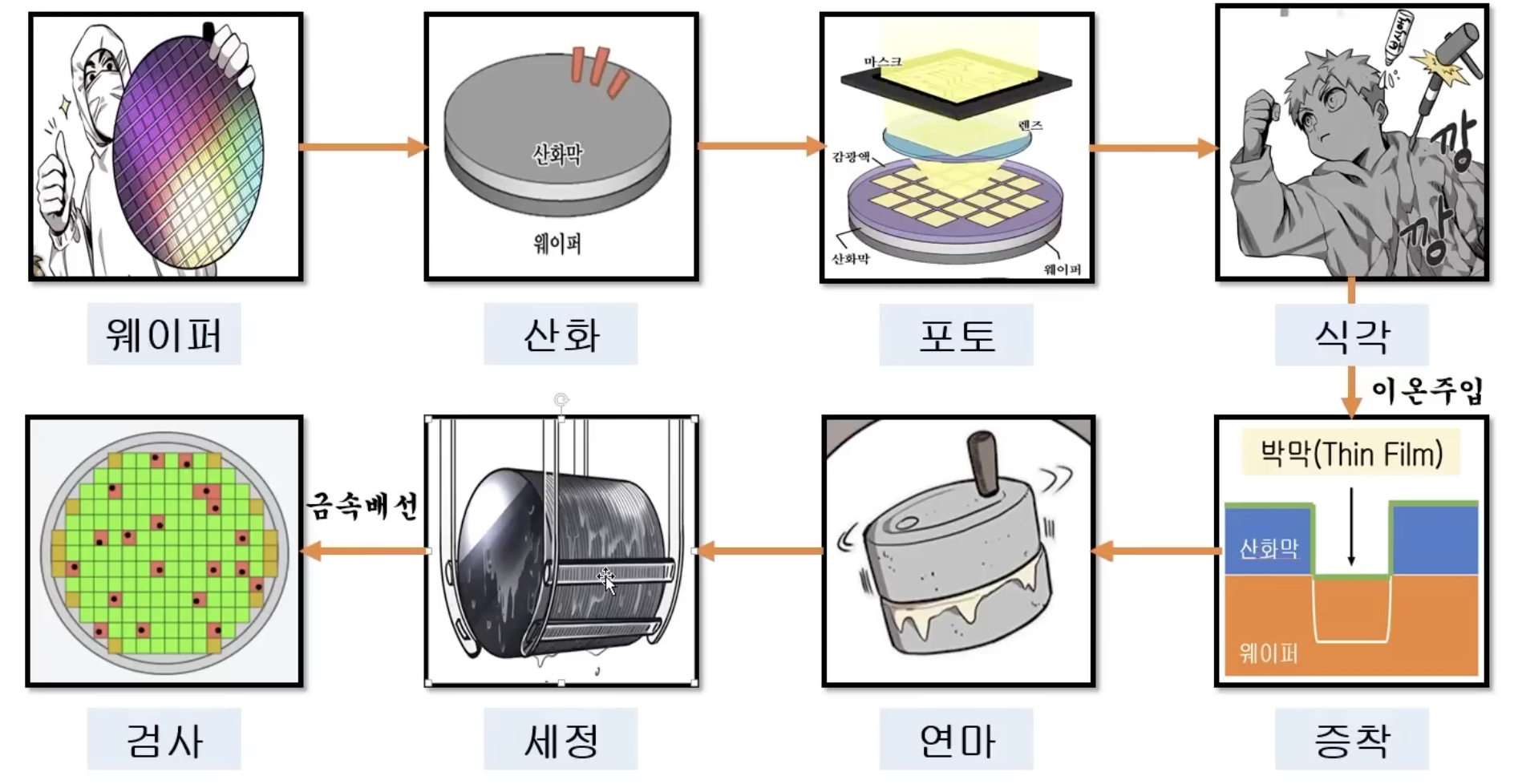

1) 반도체 8대공정

8대공정

1. 웨이퍼제조

2. 산화공정: 웨이퍼 표면에 산화막 형성

3. 포토공정(노광): 웨이퍼 위에 반도체 회로 그려 넣는 과정

4. 식각공정: 필요한 회로 패턴을 제외한 나머지 부분 제거 (산화막 제거)

5. 증착&이온주입 공정: 박막(회로 구분/연결/보호)생성, 전기적 특성 주입.

6. 금속배선공정

7. EDS공정(테스트): Electrical Die Sorting. 전기적 특성 검사 -> 개별 칩 품질 검사

8. 패키징공정: 외부환경 인터페이스 세팅.

2. 전공정 상세

웨이퍼 -> 산화 -> 포토 -> 식각 -> 이온주입/증착 -> 연마 -> 세정 -> 금속배선 -> 검사

2-1) 웨이퍼 제조

Ingot(실리콘 기둥, 잉곳)

모래 > 규소(실리콘) 추출 > 고온의 열로 용해 > 실리콘 용액 생산 > 잉곳 제조

잉곳 절단

지름 8인치,200mm(저사양) : DB 하이텍

지름 12인치,300mm(고사양 - AP,서버) : 삼성전자, TSMC

특징

장기공급계약

공급자 우위 시장 (상위 5개사)

공정기술 난이도 상승 -> 웨이퍼 수요 지속 증가

밸류체인

Shin-Etsu, SUMCO, SK 실트론, Siltronic

2-2) 산화(Oxidation)/열처리(Thermal)공정

실리콘 웨이퍼 표면에 산화막(

SiO₂) 같은 절연막을 만들거나(산화), 고온(800~1200)에서 웨이퍼 특성을 안정화/활성화(어닐링)하는 단계열산화방법

건식산화

습식산화

밸류체인

RTP 장비(급속 열처리 장비)

원익 IPS, AP 시스템

드라이 클리닝 장비 (웨이퍼 위 제거 불가능한 자연물 제거 목표)

피에스케이

2-3) 포토(노광, Photolithography)공정

가장 난이도가 높고 중요

회로 “패턴”을 웨이퍼 위에 그려넣는 단계. 포토레지스트(PR, 감광액) 도포 → 노광 → 현상으로 패턴을 만듬. (여기서

EUV가 핵심 키워드)필름역할: 포토마스크(회로설계도 그려짐)

인화지역할: 웨이퍼

감광액 -> 다만 앞으로 감광액 덜쓰거나 줄이는 기술들이 나오고 있음. 안쓰는 방향으로 갈 수 있음.

노광장비(DUV, EUV) -> 빛을 통해 웨이퍼에 회로 그리기. (빛을 선택적으로 조사)

감광액을 없어줌

DUV -> 두꺼운 빛(193, 248 광원) - ASML(80%), 니콘

EUV -> 가는 빛(13.5nm 광원) -> 7나노 이하 미세공정 - ASML(100%), 사이머(광원) - 미국회사

중국에 DUV, EUV 모두 수출 못함.

마스크 보호 -> 펠리클

밸류체인

노광 장비(EUV): ASML(사실상 독점)

포토마스크(회로 설계도): 에스앤에스텍

펠리클(마스크 보호 부품): 에스앤에스텍, 에프에스티 - EUV용은 만드는 중

감광액(웨이퍼에 도포) - 동진쎄미켐, 영창케미칼, 이엔에프테크(감광액 원료)

PR Strip - 피에스케이(감광액 제거 장비, 세계1등)

마스크 리뷰 - 파크시스템스(마스크 결함 발견, 원자현미경)

2-4) 식각(Etch, 에치)공정 - 소모성 부품 중요

포토로 만든 패턴을 “마스크”로 삼아서, 아래 막을 선택적으로 깎아내는 공정(플라즈마 식각 등)

포토공정을 거친 웨이퍼에 식각 물질 반응 -> 감광액에 보호받지 않는 부분 깎아냄.

판화 기법 - Etching 과 비슷한 원리 -부식액(etchant)을 이용해 불필요한 부분 선택적 제거.

방식

습식 -> 부식액

건식 -> 이온(플라즈마)

식각 부품

반도체 미세화 -> 가혹한 공정 환경 -> 부품 교체주기(30 -> 15) -> 부품 연간 필요량 (12 -> 30개)

Login -> 2 나노 공정

DRAM

D램은 여전히 “깊고 얇게(높은 종횡비)” 가는 싸움이라 식각/증착 난이도가 계속 올라감

1A, 1B, 1C -> 미세화 되면 식각공정이 더 들어감 (5step) -> 장비 수요 증가

3D-NAND -> 나중에 천단까지 한다면 -> HAR(고종횡비)

NAND는 DRAM보다 더 노골적으로 “3D로 높이 쌓는 게임”

적층 수가 늘어날수록 (예: 200L → 300L 방향)

구멍을 더 깊고 더 곧게 뚫고(식각), 더 균일하게 채우는(증착) 난이도가 확 올라가요.

구분1 - 쿼츠

부품중에서 가장 규모가 크다. 소모성

웨이퍼를 불순물 및 충격으로부터 보호하는 용기에 사용

천연쿼츠: 석영 유리로 이루어짐, 웨이퍼 보호

합성쿼츠: 천연쿼츠 단점 보완, 투과성 좋고, 수명 길다

구분1 - 파츠(Si, SiC 포커스링)

식각장비 내 플라즈마(건식 식각)를 웨이퍼 안으로 안정적으로 모아주고, 플라즈마 밀도를 균일하고 정확하게 유지시켜주는 역할. 소모성 부품

Si 파츠: 파츠중에 가장 많이 씀, 식각 장비 상하단에 사용, D램 위주, 100만원(쌈), 고온 강한데 강도 약함,

SiC파츠

NAND 위주, 삼성전자는 거의 1000단까지 -> SiC파츠 점점커짐, 250만원(비쌈), 강도 강함, 비싼대 제조 어려움 - 아무나 못함.

구분2 - Before Market (장비회사 직접 납품, 고마진)

티씨케이(SiC Ring 최초 개발) -> Applied Materials(AMAT), Lam Research(LRCX) 납품

하나머티리얼즈(Si, SiC) -> Tokyo ...