1. 패키징

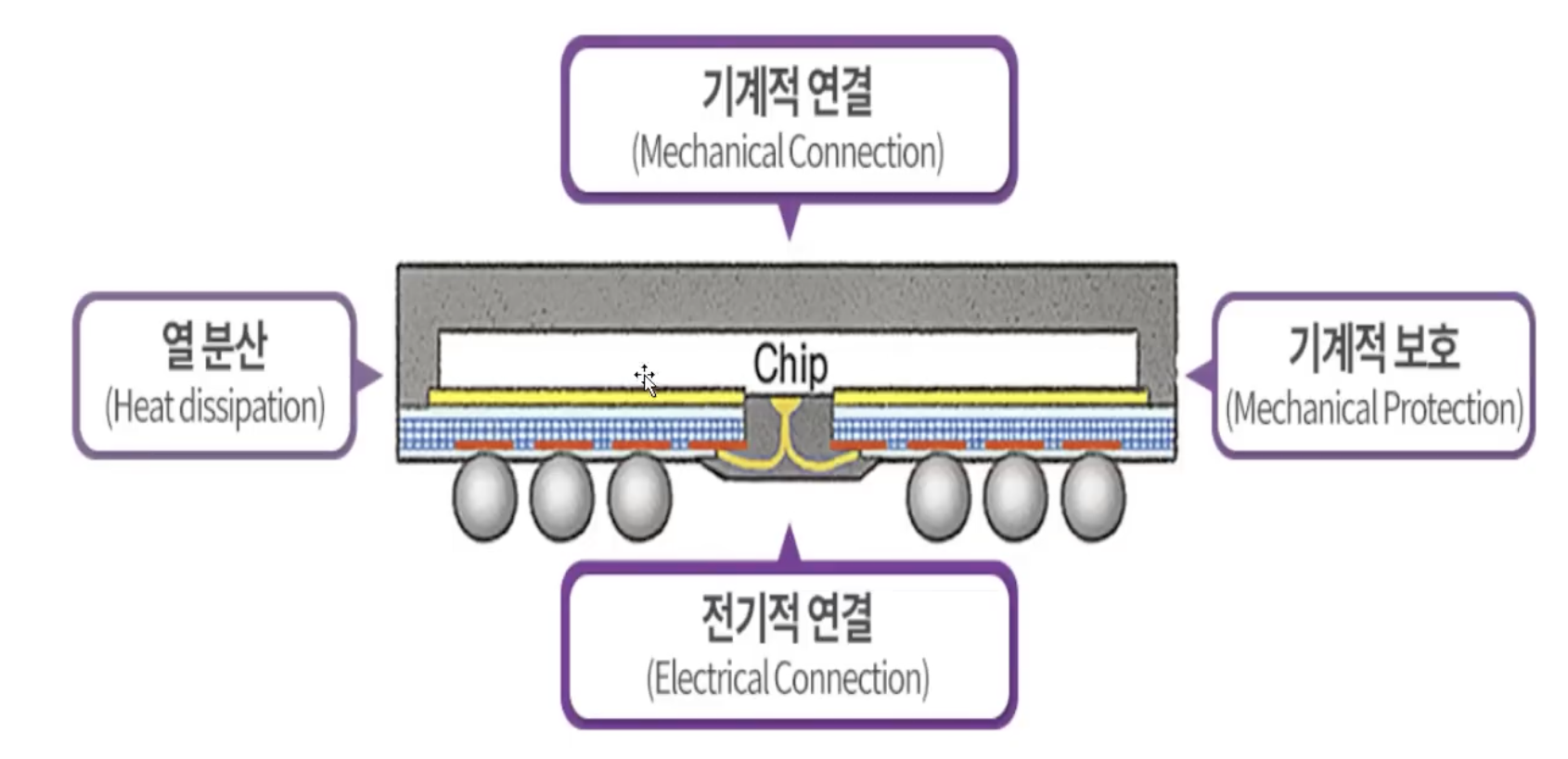

패키징: 칩을 보호하고 연결, 반도체로 사용 가능하게 최종 점검

라미네이션(Lamination): 웨이퍼에 테이프(보호막) 부착

백그라인드(Back Grind): 평탄하게, 웨이퍼 후면

다이싱(Wafer Saw): 웨어퍼에 있는 칩 절단 -

이오테크닉스,한미반도체칩 접착(Die Attach): 칩을 PCB위에 옮김

본딩(Bonding): 칩과 기판 - 전기적 연결

금속 와이어 -

엠케이전자3D본딩 -

한미반도체리드프레임(지지대) -

해성디에스(자동차용으로 많이 만듬)숄더볼 -

덕산하이메탈플립칩 -

대덕전자

몰드(Mold): 칩 보호막(에폭시) 형성

마킹(Marking): 제품명 새기기 -

이오테크닉스숄더볼 마운트(Solder Ball Mount): 숄더볼(조그만 공) -> 평평하게 펴주고 붙임

숄더볼과 잘 붙을 수 있게 리플로우(평평하게) -

피에스케이홀딩스,에스티아이

싱귤레이션(Singulation): 칩 각각 자르기.

1-1. 본딩

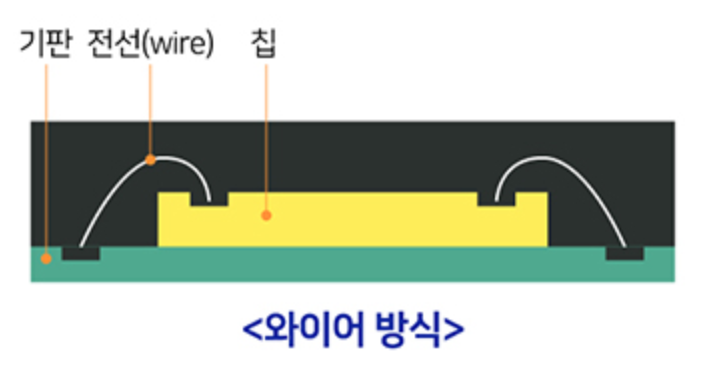

1) 와이어 본딩

경쟁 포인트 - UPH(처리량), 원가, 범용 물량

강점: 공정이 성숙했고 단가가 낮고, 범용 패키지에서 여전히 물량이 큼

한계: 고속·고전력·초미세 피치에는 구조적으로 불리

(배선이 길어져 신호 손실/노이즈/전력 무결성에서 손해)

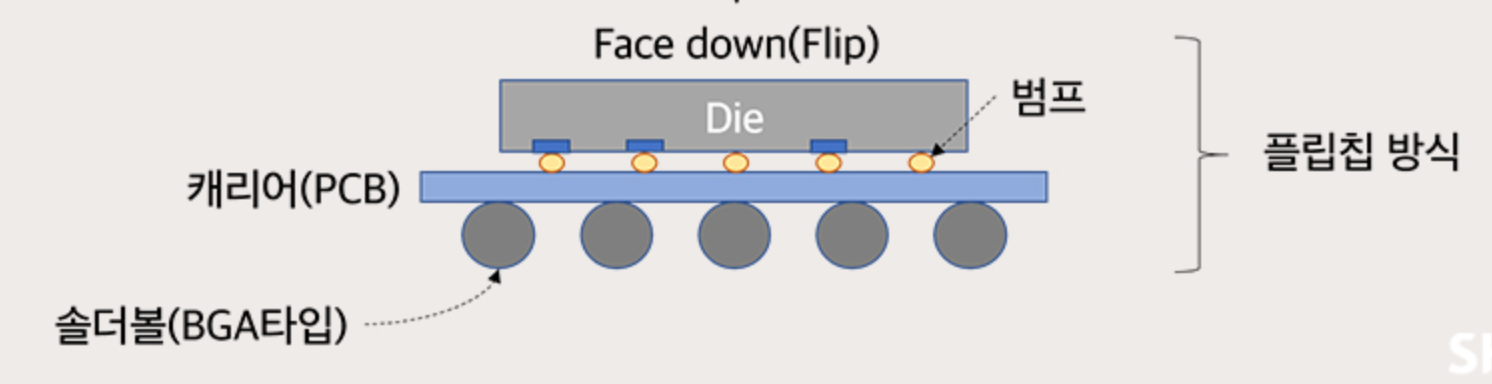

2) 플립 칩(Flip Chip, FC)

경쟁포인트 - 정렬 정밀도, 범프 피치, 기판/언더필/워페이지 관리

다이를 뒤집어서(Flip) 기판/인터포저 쪽에 범프(Bump)로 직접 연결

장점: 와이어보다 경로가 짧아 고속/고전력에 유리, I/O를 촘촘히 깔기 좋음

단점: 공정 복잡도↑, 기판/언더필/뒤틀림 등 패키지 설계 난이도↑

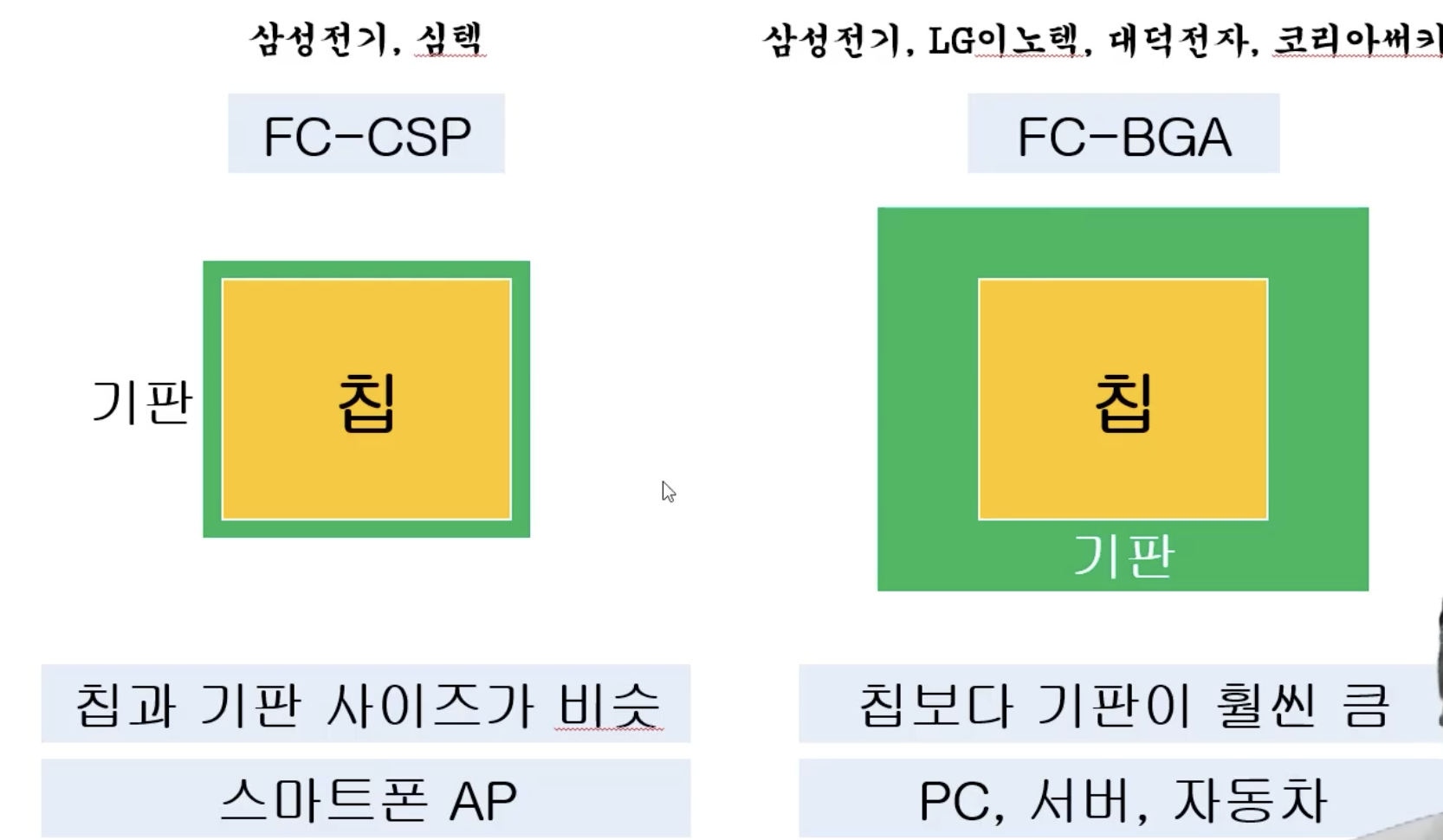

CSP vs BGA

FC-CSP(Chip Scale Pacakge)

칩과 기판 크기가 비슷 -> 작다 -> 스마트폰

삼성전기,심텍

FC-BGA(Ball Grid Array)

칩보다 기판이 훨씬 큼 -> PC, 서버

삼성전기,LG이노텍,대덕전자,코리아써키트

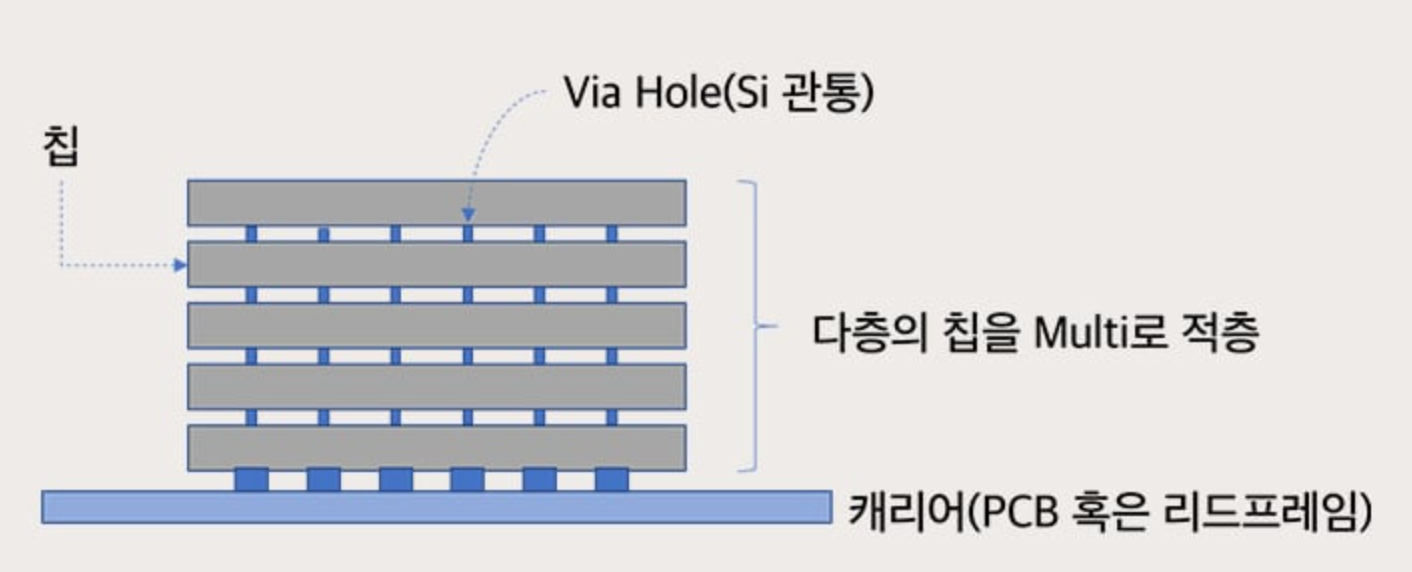

3) 3D 본딩, TSV(Through-Silicon Via) 기술

여러 개의 다이(Die)를 위로 쌓거나(메모리 스택), 서로 아주 가까이 붙여서(로직-메모리 근접) 연결 밀도와 전력/신호 성능을 극대화

핵심

피치(pitch)가 얼마나 줄어드나(= 연결을 얼마나 촘촘히 할 수 있나)

수율(Yield)을 얼마나 안정적으로 뽑나

Throughput(시간당 처리량) vs 수율 트레이드오프를 누가 먼저 풀었나

본딩 방식 진화

μ-bump(마이크로범프) 기반 적층/연결TCB(Thermo-Compression Bonding, 열압착)로 더 정밀/고신뢰 연결 -한미반도체정렬+압력+열 프로파일+throughput의 동시 최적화(가장 어려운 축 중 하나)

(차세대)

Hybrid Bonding(Cu-Cu + oxide)로 범프를 줄이거나 사실상 없애면서 피치를 더 줄이는 방향 -한화 비전표면 평탄/클린/정렬/접합 결함(보이드) 관리가 핵심이고 “양산 레퍼런스”가 전부

TSV 기술

TSV - 실리콘 다이(특히 DRAM 다이)를 “관통”해서 위아래 다이를 전기적으로 연결하는 수직 배선

HBM은 여러 장의 DRAM 다이를 스택으로 쌓고, 그 사이를

TSV로 연결해서 대역폭을 크게 끌어올리는 구조가 기본투자자 관점에서 TSV는 “공정이 한두 개”가 아니라 밸류체인(장비/소재/공정) 묶음

공정 흐름: Via를 뚫기(Deep etch) → 절연막/배리어/시드 증착 → 구리 채우기(plating) → CMP로 평탄화 → 웨이퍼 얇게 갈기(thinning) → 후속 본딩/검사

1-2. 반도체 기판 & 밸류체인

본딩: 칩과 - '기판' 연결. 기판 좀더 딥다이브

1) 패키지 기판(서브스트레이트) - 칩 바로 아래 들어가는 기판

FC-CSP(Chip Scale Pacakge)

칩과 기판 크기가 비슷 -> 작다

모바일이 드라이브

삼성전기,심텍

FC-BGA(Ball Grid Array)

칩보다 기판이 훨씬 큼 -> PC, 서버

AI 서버/네트워크가 드라이브

삼성전기,LG이노텍,대덕전자,코리아써키트

2) 시스템 PCB - 완제품 안의 메인 보드/서버 PCB

SiP(System in Package)

스마트폰 RF 프론트엔드, 웨어러블, IoT, 자동차(센서/통신) 쪽에서 “작고 얇게”가 핵심일 때

심택,삼성전기,LG이노텍

HDI(High Density Interconnect, 고밀도 다층 기판)

모바일이 드라이브

코리아써키트,디에이피

RF-PCB(Rigid-Flexible PCB)

Rigid(딱딱한 PCB) + Flexible(휘어지는) PCB 혼합

비에이치-> 애플,뉴플렉스-> AR,VR,인터플렉스

MLB(Multi Layer Board)

기판이 여러층으로 이루어진 다층(4층 이상) PCB

모바일이 드라이브

이수페타시스,대덕전자

3) 모듈 PCB

D램(DDR5), NAND Flash(SSD), 신규아이템(PCB)

티엘비,심텍

4) 리드프레임 - 금속 프레임 기반(전력/아날로그 패키지에 많음)

Lead - 반도체 칩과 외부 회로를 전기적으로 연결

Frame - 칩을 지지해주는 기판 역할

자동차/산업이 드라이브

해성디에스

2. 후공정(패키지) 테스트 - 소켓과 검사공정

2-1. 반도체 검사(테스트) 전 과정

`전공정 -> 웨이퍼 번인 ...

![[산업 > 반도체] 시스템 반도체(파운드리), 메모리반도체(D램, 낸드)](https://post-image.valley.town/QL-lMg7w0Ox9qLeLq8QeR.png)

![[산업>반도체] 종류/8대공정/전공정 밸류체인](https://post-image.valley.town/2X4yEK6Y16q6-1tOeMllO.png)