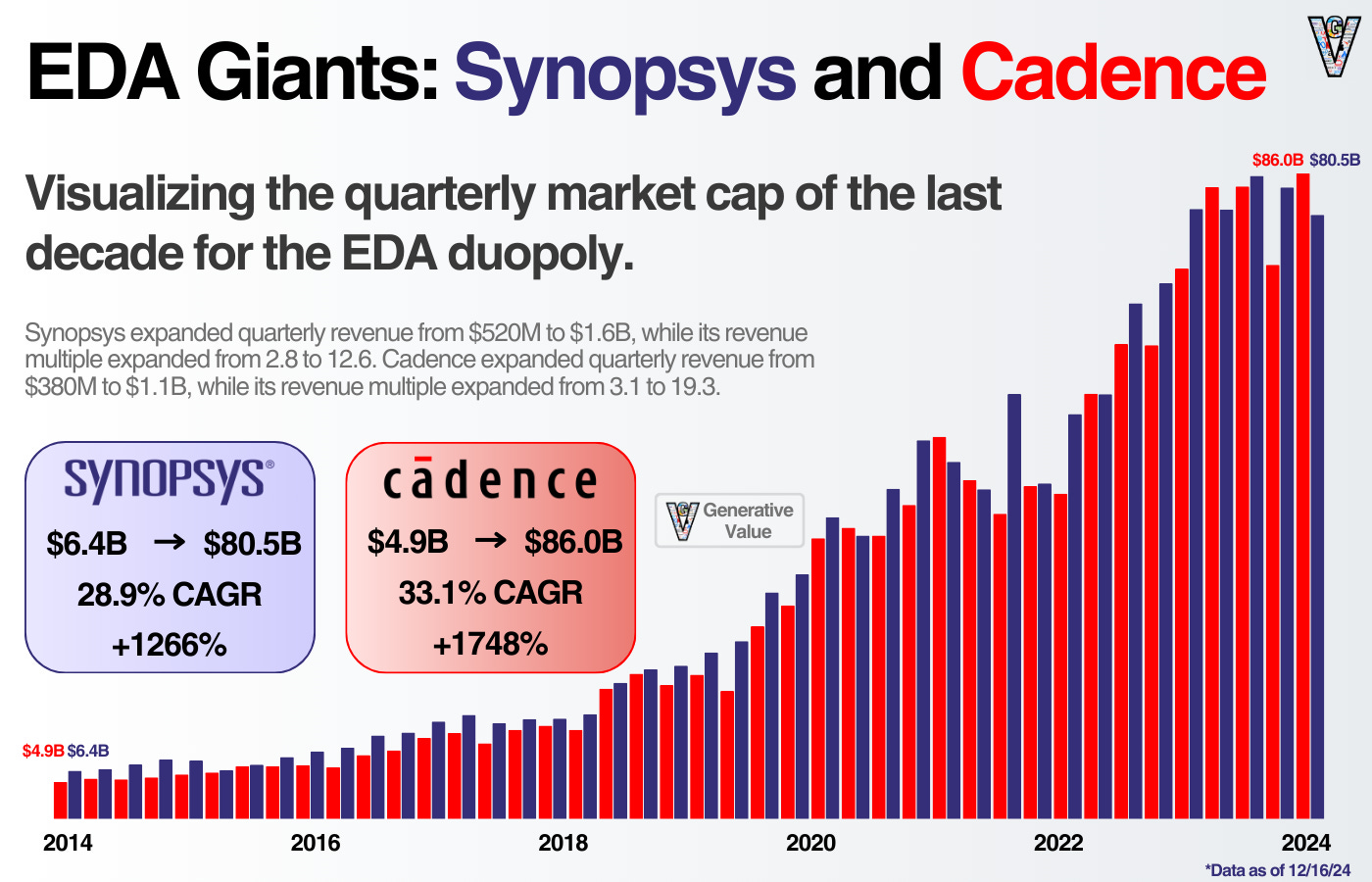

케이던스와 시놉시스는 지난 10년간 세계에서 가장 수익률이 좋은 주식 중 두 곳입니다. Cadence와 Synopsys의 연간 수익률은 각각 33%와 29%입니다(배당금 제외).

이 두 회사는 미국의 중요한 전략적 자산일 뿐만 아니라 세계에서 가장 방어력이 뛰어난 소프트웨어 회사 중 하나가 되었습니다.

오늘날 이들의 이야기는 매우 긍정적입니다. 10~15년 전에는? 앞으로 나아갈 길은 그렇게 명확하지 않았습니다.

특히 2000년대 들어 가격 책정과 실행에 어려움을 겪었던 케이던스는 KKR의 사모펀드 인수를 검토하는 지경에 이르렀습니다. 2009년 립-부 탄이 회사를 인수했고, 그 이후 주가는 대부분 상승세를 타고 있습니다.

진정한 기대치 투자 스타일에서는 낮은 기대치 + 훌륭한 펀더멘털 성과가 놀라운 수익률 상황을 만들어 냈습니다.

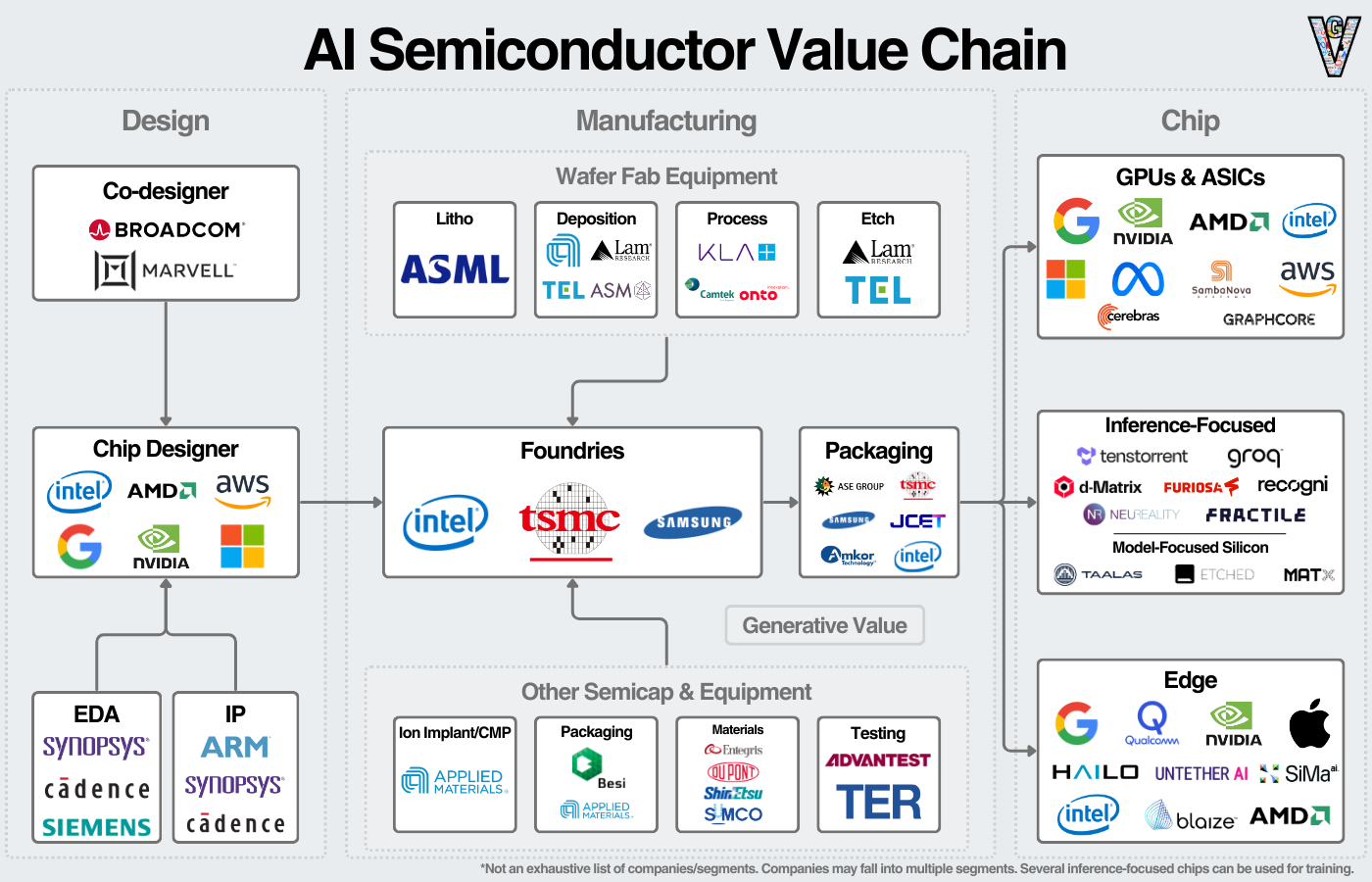

“당신이 들어본 적 없는 가장 중요한 회사"라는 표현이 과장된 측면이 있지만, Synopsys와 Cadence Design Systems는 확실히 그 대화에 포함될 수 있습니다. 이 두 회사는 Siemens EDA와 함께 반도체 설계에 사용되는 소프트웨어인 전자 설계 자동화(EDA) 산업에서 독과점적 지위를 누리고 있습니다.

전 세계 모든 주요 반도체 회사가 이 소프트웨어를 사용합니다. 즉, 우리가 사용하는 모든 주요 기술은 이 회사들에 의존하고 있습니다.

그 덕분에 Synopsys와 Cadence는 (1) 지난 10년간 시장에서 가장 높은 수익률을 기록했고, (2) 시장에서 가장 높은 밸류에이션을 받았습니다.

이 글은 전자 설계 자동화(EDA) 산업과 주요 업체, 그리고 그 미래에 대한 여러 편의 시리즈 중 첫 번째 글입니다.

1. EDA의 개요 및 반도체 에코시스템에서의 위치

전자 설계 자동화(EDA) 툴은 반도체를 설계하는 데 사용되는 소프트웨어입니다. Nvidia와 같은 반도체 설계 회사는 이러한 도구를 사용하여 칩을 설계하고 TSMC에서 제작하기 전에 성능을 시뮬레이션합니다.

또한 반도체 IP의 '빌딩 블록'도 판매합니다. 기업이 칩을 설계할 때 Wi-Fi 및 USB 상호 작용을 다시 설계하는 대신 해당 기능에 대한 IP를 구입하여 설계에 포함시킬 수 있습니다. 아래에서 생태계 내에서의 위치를 확인할 수 있습니다:

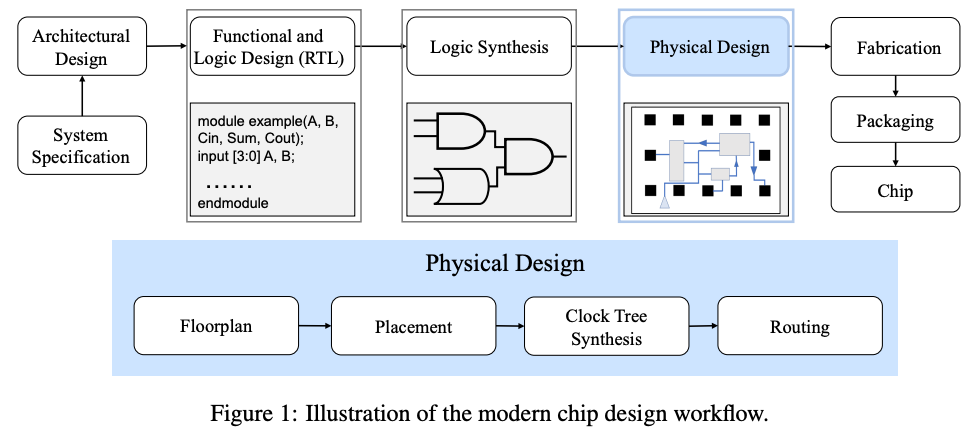

반도체를 설계하는 과정은 다음과 같습니다:

1. 요구 사항 수집 및 시스템 설계

다른 물리적 제품과 마찬가지로 칩 설계의 첫 번째 단계는 칩이 달성해야 하는 목표를 정의하는 것입니다. 칩이 무엇을 하고, 어떻게 사용될 것이며, 이러한 목표를 달성하기 위해 어떤 성능 메트릭을 충족해야 할까요? 이 모든 것은 고객이 요구하는 사항과 칩의 사용 사례에 따라 결정됩니다.

기업은 설계로 넘어가기 전에 모든 요구 사항이 포함된 사양서를 정의합니다.

2. 로직 설계 및 RTL(레지스터 전송 레벨) 코딩

다음으로 디자이너 팀이 로직 또는 회로 설계를 시작합니다. 이들은 칩의 상위 레벨 빌딩 블록을 지정하고 Verilog와 같은 코딩 언어를 사용하여 해당 빌딩 블록의 로직을 정의합니다.

이러한 빌딩 블록에는 논리 회로, 메모리 회로, 칩 안팎의 데이터 흐름을 관리하는 입출력 인터페이스와 같은 블록이 포함됩니다. 예를 들어, 로직 블록에는 여러 메모리 블록의 데이터가 필요하며 이러한 작업은 칩 전체에서 동기화되어야 하므로 RTL 설계는 데이터가 칩을 통해 어떻게 흐르는지 정의해야 합니다.

최종 결과는 로직 및 메모리 회로가 함께 배선된 '청사진'입니다.

3. 로직 합성

칩은 모든 회로를 수작업으로 설계하기에는 너무 복잡하기 때문에 설계자는 로직 합성 도구를 사용하여 RTL 코드를 칩의 논리적 표현을 만드는 게이트의 '넷리스트'로 변환합니다. 이러한 게이트는 반도체가 정보를 처리할 수 있는 경로를 생성하며, (AND, OR, NOR) 및 플립플롭(1 또는 0 상태의 메모리 유닛)과 같은 논리 함수로 구성됩니다:

4. 물리적 회로 설계

논리 설계가 끝나면 넷리스트는 네 가지 주요 단계로 구성된 물리적 설계로 넘어갑니다: 플로어플랜, 배치, 클록 트리 합성, 라우팅입니다.

플로어플래닝은 전선 길이, 면적, 전력 소비를 최소화하기 위해 칩에 큰 블록(로직, 메모리)의 대략적인 위치를 배치하는 단계입니다. 배치는 대형 블록 내에서 셀(로직 게이트 및 플립플롭)의 정확한 위치를 결정합니다.

클록 트리 합성은 회로의 데이터 흐름을 타이밍에 맞게 최적화하기 위해 분배 네트워크를 생성합니다. 예를 들어 논리 회로에 여러 메모리 유닛의 데이터가 필요한 경우 데이터가 동시에 논리 회로에 도착해야 합니다. 데이터 버퍼 또는 인버터를 삽입하여 칩 전체에 클럭 신호를 분배합니다. 마지막으로 라우팅은 칩에 배선을 배치하여 전선 길이를 최소화하고 칩 내의 '누화' 및 '기생' 효과를 최소화합니다.

5. 시뮬레이션, 검증 및 검증

칩이 설계되면 성능 요구 사항을 충족하고 TSMC와 같은 팹의 설계 규칙을 위반하지 않는지 확인하기 위해 시뮬레이션을 실시합니다.

칩은 설계 규칙 검사, 레이아웃 검증, 타이밍 분석, 파운드리 규칙 분석 등 여러 검증 단계를 거칩니다. 규칙을 위반하는 경우 설계를 수정하고 다시 검증합니다.

설계 결함으로 인한 비용은 수천만 달러에 달하며, 제품 출시가 지연될수록 수억 달러로 늘어날 수 있습니다.

검증은 반도체 설계의 주요 병목 현상 중 하나이며, 일반적으로 설계자 한 명당 1~2명의 검증 엔지니어가 있습니다. 이러한 높은 수요와 빠른 반도체 제품 주기로 인해 검증 엔지니어에 대한 인재 부족 현상이 심각합니다.

6. *보너스: PCB 설계:

PCB(인쇄 회로 기판) 설계는 반도체를 더 넓은 ...

![[IT] AI 데이터 센터에 대한 입문서, 2부: 에너지 from EricFlaningam](https://substackcdn.com/image/fetch/w_1456,c_limit,f_auto,q_auto:good,fl_progressive:steep/https%3A%2F%2Fsubstack-post-media.s3.amazonaws.com%2Fpublic%2Fimages%2F64f40bf1-71b2-4c53-b141-589e1ae727bd_1272x821.png)